# Design and Simulation of UART Module with BIST Techninque

#### Girdhar Gopal, Rashmi Chawla

**Abstract**— In the life cycle of a VLSI device including VLSI development process, testing is performed at various stages. Testing results into production of defect free device. BIST is a technique that allows a system to test automatically itself. BIST generate test pattern automatically, so it can provide less time as compared to an externally applied test pattern and helps to achieve more productivity at the end. Universal Asynchronous Receiver transmitter (UART) is programmable module that is primarily used for asynchronous serial communication. UART module with BIST technique is designed in verilog HDL and Xilinx is used for synthesis and simulation. This design eliminate need for higher expensive tester and offers promising approach for data exchange with reduced development time and cost.

----- 🌢 ------

Index Terms — BIST, LFSR, MISR, Simulation, Synthesis, UART, Xilinx, Verilog HDL

## **1** INTRODUCTION

${

m A}\,$  UART (Universal aynchronous receiver transmitter) is

serial communication programmable module which handle data exchange between processor and peripherals. It handle data conversion between parallel and serial data. Basic UART communication needs only two signal signal lines(TXD,RXD) in order to complete full duplex data communication[1,2,3].

TXD is transmitter side output of UART; RXD is receiver side input of UART. UART serial communication module is divided into three submodule: transmitter, receiver and baud rate generator[3, 4]. Each and every module is responsible for its own task. Failure in any one of module affects overall output of UART.The basic job of UART is converting data from parallel to serial for transmission and serial to paralllel on reception[5]. In actual application, usually only a few key features of UART are needed[6].

Manufacturing processes are extremely complex, inducing manufacturer to consider testability as requirement to assure the reliability and functionality of each of their design circuits. Testing of Integrated circuits(Ics) is important to ensure a high level of quality in product functionality in both commercially produced and privately produced products[6].

Built in self test or BIST is a technique in which parts of a circuit are used to test the circuit. BIST architecture consists of linear feedback shift register (LFSR) ,circuit under test and comparator unit. The objective of BIST is to reduce power dissipation.

Main areas in VLSI are performance, cost, testing, area,

reliability and power. The demand for portable computing devices are increasing rapidly.

BIST is DFT( design for testability) methology aimed at detecting faulty components in a system by incorporating test logic on chip [7]. In this paper, internal diagnostic capabilities are built into UART with help of BIST.

The paper is organised into 5 sections. Section 2 explains BIST architecture . Section 3 explains UART architecture with BIST. Section 4 presents result and section 5 provides conclusion of work.

## **2 BIST ARCHITECTURE**

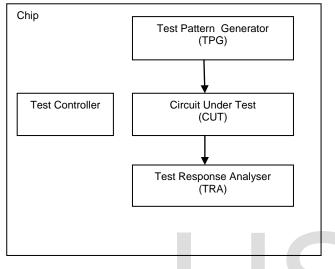

VLSI testing problems like test generation problems, input combinatorial problems and the gate to I/O problem are discussed and this motivated the designers to identify reliable test methods in solving these difficuties. An insertion of special test circuitry on the VLSI circuit that allows efficient test coverage is answer to the problem. It is addressed by need of design for testability (DFT) using BIST circuit. BIST is an on-chip test logic that is utilized to test the functional logic of a chip, by itself. With rapid increase in design complexity, BIST has become a design consideration in DFT methods and is becoming more popular in today' s state of art SoCs( system on a chip). A popularly designed BIST is able to offset the cost of added test hardware while at the same time ensuring the reliability, testability and reduces maintenance cost. BIST solution consists of an automatic test pattern generator(ATPG), circuit to be tested, a way to analyse the result and a way to compress the result for simplicity. In BIST, a test logic circuit is incorporated in the chip[8]. The extra circuit generates test patterns, applies them to the inputs and the tests the circuit. This extra circuit increases the chip size but reduces the test cycle time. Fig 1 shows BIST module composition.

Girdhar Gopal is currently pursuing M.Tech (VLSI) in YMCA University, Faridabad, India, E-mail: gautam.girdhargopal47@gmail.com

<sup>•</sup> Rashmi Chawla is assistant professor in YMCA University, Faridabad, India, E-mail: rashmichawlaymca@gmail.com

Components of BIST are :

Test pattern generator(TPG) : It is a circuit which is to be tested. It can be a microprocessor or a dedicated circuit. Mostly patten used is pseudorandom pattern.

Circuit under test (CUT) : It is a part of circuit that is to be tested. It can be sequential, combinational or memory.

Test Response Analyser(TPA) : It analyses the value sequence on input and compare it with expected output.

Test controller: It control the test execution, it manages TPG, CUT and TRA.

Fig. 1 BIST module composition

### 2.1 Linear feedback shift register(LFSR)

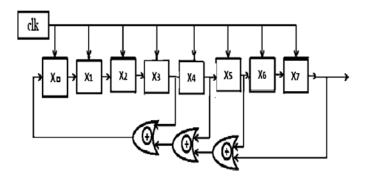

LFSR is used to generate pseudorandom testvectors in the chip. It is mainly used test pattern generator(TPG). THE output at each stage of an lfsr are used as input of circuit. The LFSR is clocked for a large number of cycles and output is monitored. It is implemented with shift register and Ex-OR gate[9,10]. Fig 2 Shows 8-bit LFSR.

Fig. 2 8-bit LFSR

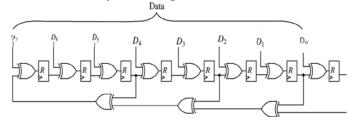

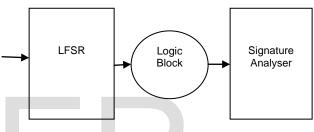

### 2.2 Multiple input signature analysis register (MISR)

MISR is one which can be used to reduce the amount of hardware required. MISR is used to compress the mutiple bit stream. The compressed response is referred to as signature of the device under test.its output developes a signature based on the effects of all the bits fed into it [11]. A signature analyser is formed by adding extra XOR gates at input of LFSR[8]. A test input sequence is applied at the input and the resulted output sequence is compared with the signature to determine a faulty circuit. Fig. 3 shows MISR structure.

Fig. 3 MISR structure

#### 2.3 Buit-in block observer(BILBO)

A signature analyser and scan test circuit is combined to form a buit-in block observer (BILBO)[11].

Fig. 4 Blockdiagram of BILBO

Bilbo is a scan register that can be modified to serve as a state register, a pattern register or a shift register.

TABLE 1 BILBO OPERATING MODES

| s1 | s0 | Operating Mode |

|----|----|----------------|

| 0  | 0  | Shift Register |

| 0  | 1  | LFSR           |

| 1  | 0  | Normal         |

| 1  | 1  | MISR           |

# **3 UART ARCHITECTURE WITH BIST**

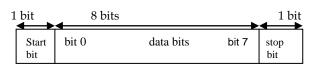

UART frame format or serial package consists of start bit , input data , optional parity bit and stop bit. Fig. 5 shows frame format or serial package(excluding parity bit) [12].

Fig. 5 UART serial Package(excluding parity bit)

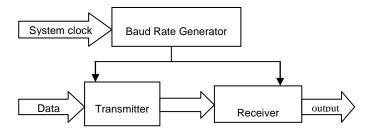

UART frame is decided initially and then communication process is started[13,14]. UART serial communication module is divided into three submodule: transmitter, receiver and baud rate generator[14]. Fig. 6 shows UART Block Diagram. Each and every module is responsible for its own task. Failure in any one of module affects overall output of UART.The basic job of UART is converting data from parallel to serial for transmission and serial to parallel on reception[15,16].

Fig. 6 UART Block Diagram

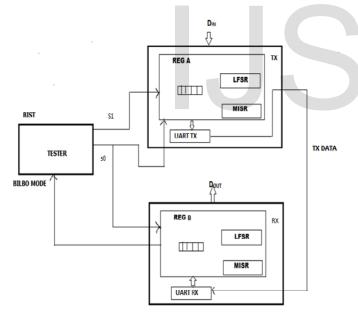

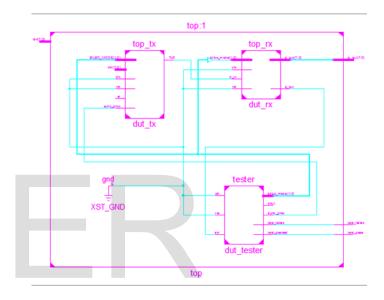

The basic job of UART is converting data from parallel to serial for transmission and serial to parallel on reception[16]. Fig. 7 Shows block diagram of UART with BIST. There are three essential components of UART : transmitter , receiver and tester.

#### Fig. 7 block diagram of UART with BIST

The function of transmitter module is to convert the 8-bit parallel data into serial data, addition of start bit at the head of data as well as parity bit and stop bit at the end of data.The function of receiver module is to convert serial data into 8-bit parallel data. Receiving unit is responsible for sampling the incoming data and extracting the symbol from the received frame of bits [17]. Baud rate generator is actually a frequency divider. It generate pulse of one cycle periodically, according to baud rate configured [17]. Typical baud rate values are 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600,115200.

### **4 SYNTHESIS AND SIMULATION RESULTS**

Xilinx ISE is (Integrated software environment) is a software tool produced by Xilinx for synthesis and analysis of HDL designs, which enable the developer to synthesize their design, perform timing analysis, examine RTL diagram, simulate a design's reaction to different stimuli and configure target device with programmer.

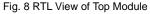

### 4.2 Simulation of transmitter

The simulation shows the transmission of an 8- bit UART frame format with 1 stop bit and without a parity bit. The transmission was set at 115.2 Kbps using 40MHz clock, which is equal to 25ns( 1/40MHz = 25ns Fig. 9 shows the transmission of 8-bit data ( "10011111") via DATA[7:0]. The transmitted Uart frame format can be observed at TXD ( 1 low start bit, 8 data bits and 1 high stop bit).

Fig. 11 Transmitter Simulation

# 4.3 Simulation of Receiver

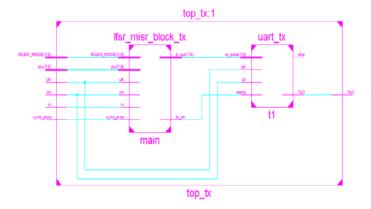

Fig. 13 shows how an 8-bit serial data from RXD is received.

Fig. 12 Receiver Simulation

# 4.4 Simulation of UART with BIST

FIg.14 shows simulation of UART with BIST

Fig. 13 UART Simulation with BIST

### 4.5 Design Summary of UART

The report after optimization process will be used as basis for comparison of UART design before and after implimentation of BIST technique. International Journal of Scientific & Engineering Research, Volume 8, Issue 4, April-2017 ISSN 2229-5518

| Design Summary:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Additional JTAG gate count for IOBs: 1344                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of errors: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                |

| Number of warnings: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timing summary:                                                                                                                                                                                                                                                                                                                                                |

| Number of CLBs: 160 out of 196 81%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                |

| CLB Flip Flops: 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Timing errors: 0 Score: 0                                                                                                                                                                                                                                                                                                                                      |

| 4 input LUTs: 279 (1 used as route-throughs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                |

| 3 input LUTs: 49 (16 used as route-throughs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Constraints cover 2523 paths, 373 nets, and 1235                                                                                                                                                                                                                                                                                                               |

| Number of bonded IOBs: 28 out of 61 45%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | connections (100.0% coverage)                                                                                                                                                                                                                                                                                                                                  |

| IOB Flops: 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                |

| IOB Latches: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |

| Number of clock IOB pads: 1 out of 8 12%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                |

| Number of primary CLKs: 1 out of 4 25%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Design statistics:                                                                                                                                                                                                                                                                                                                                             |

| Number of secondary CLKs: 1 out of 4 25%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Minimum period: 28.678ns (Maximum frequency:                                                                                                                                                                                                                                                                                                                   |

| Number of TBUFs: 3 out of 448 1%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34.870MHz)                                                                                                                                                                                                                                                                                                                                                     |

| Number of startup: 1 out of 1 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Maximum combinational path delay: 33.437ns                                                                                                                                                                                                                                                                                                                     |

| realized and re | Maximum net delay: 11.823ns                                                                                                                                                                                                                                                                                                                                    |

| Fotal equivalent gate count for design: 2789                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                |

| (a) UART without I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BIST Design Summary                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                |

| Design Summary:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (2% of the CLBs used are affected.)                                                                                                                                                                                                                                                                                                                            |

| Design Summary:<br>Number of errors: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289                                                                                                                                                                                                                                                                            |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (2% of the CLBs used are affected.)                                                                                                                                                                                                                                                                                                                            |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2<br>Number of LBs: 190 out of 196 96%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289                                                                                                                                                                                                                                                                            |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Filp Flops: 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289                                                                                                                                                                                                                                                                            |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680                                                                                                                                                                                                                               |

| Design Summary:<br>Number of errors: 0<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:                                                                                                                                                                                                            |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680                                                                                                                                                                                                                               |

| Design Summary:<br>Number of errors: 0<br>Number of Varmings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br><br>Timing errors: 0 Score: 0                                                                                                                                                                           |

| Design Summary:<br>Number of errors: 0<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br><br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498                                                                                                                       |

| Design Summary:<br>Number of errors: 0<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br><br>Timing errors: 0 Score: 0                                                                                                                                                                           |

| Design Summary:<br>Number of errors: 0<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0<br>Number of Latches: 0<br>Number of primary CLKs: 1 out of 8 12%<br>Number of primary CLKs: 1 out of 4 25%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br><br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498                                                                                                                       |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 342 (1 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0<br>Number of Clock IOB pads: 1 out of 8 12%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498<br>connections (100.0% coverage)<br>Design statistics:                                                                    |

| Design Summary:<br>Number of errors: 0<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0<br>Number of Latches: 0<br>Number of primary CLKs: 1 out of 8 12%<br>Number of primary CLKs: 1 out of 4 25%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498<br>connections (100.0% coverage)<br>Design statistics:                                                                    |

| Design Summary:<br>Number of errors: 0<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 54 (18 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0<br>Number of clock IOB pads: 1 out of 8 12%<br>Number of primary CLKs: 1 out of 4 25%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498<br>connections (100.0% coverage)<br>Design statistics:                                                                    |

| Design Summary:<br>Number of errors: 0<br>Number of warnings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 342 (1 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0<br>Number of clock IOB pads: 1 out of 8 12%<br>Number of primary CLKs: 1 out of 4 25%<br>Number of storder, CLKs: 1 out of 4 2%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br><br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498<br>connections (100.0% coverage)<br>Design statistics:<br>Minimum period: 31.270ns (Maximum frequency:                |

| Design Summary:<br>Number of errors: 0<br>Number of Varmings: 2<br>Number of CLBs: 190 out of 196 96%<br>CLB Flip Flops: 158<br>4 input LUTs: 342 (1 used as route-throughs)<br>3 input LUTs: 342 (1 used as route-throughs)<br>Number of bonded IOBs: 35 out of 61 57%<br>IOB Flops: 2<br>IOB Latches: 0<br>Number of clock IOB pads: 1 out of 8 12%<br>Number of primary CLKs: 1 out of 4 25%<br>Number of primary CLKs: 1 out of 4 25%<br>Number of secondary CLKs: 1 out of 4 25%<br>Number of startup: 1 out of 1 100%<br>4 unrelated functions packed into 4 CLBs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (2% of the CLBs used are affected.)<br>Total equivalent gate count for design: 3289<br>Additional JTAG gate count for IOBs: 1680<br>Timing summary:<br><br>Timing errors: 0 Score: 0<br>Constraints cover 2848 paths, 443 nets, and 1498<br>connections (100.0% coverage)<br>Design statistics:<br>Minimum period: 31.270ns (Maximum frequency:<br>31.980.Hfz) |

Fig. 14 Design Summary of UART

#### **5** CONCLUSION